|

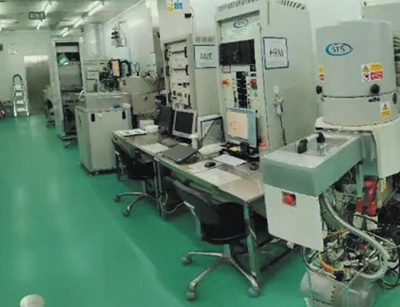

北京大学微电子工艺实验室一角。 |

党的二十大报告提出:“必须坚持科技是第一生产力、人才是第一资源、创新是第一动力,深入实施科教兴国战略、人才强国战略、创新驱动发展战略,开辟发展新领域新赛道,不断塑造发展新动能新优势。”

青年强,则国家强。党的十八大以来,一大批70后、80后、90后青年科研人员脱颖而出,日益成为科技创新的生力军、主力军。他们怀抱梦想又脚踏实地,敢想敢为又善作善成,展示了自信自强、勇攀高峰、蓬勃向上的中国力量。本版从今天起推出“科技自立自强 青年奋勇担当”系列报道,介绍优秀青年科学家的创新成果和科研故事,敬请关注。

——编 者

人物简介:

黄芊芊,1989年9月生于江西上饶,现为北京大学集成电路学院研究员、博士生导师,长期致力于后摩尔时代超低功耗微纳电子器件及其应用研究。

16岁考入北大,22岁在国际半导体技术领域顶级会议“国际电子器件大会”上发表论文,28岁成为北京大学研究员、博导,29岁获得国家优秀青年科学基金项目资助,30岁荣获美国电气与电子工程师协会电子器件学会青年成就奖、中国求是杰出青年学者奖,31岁荣获第二届腾讯科学探索奖,而且是50名获奖者中年龄最小的一位……

30出头的黄芊芊,是如何一路过关斩将、脱颖而出的?

黄芊芊读大三时加入黄如院士课题组,大四毕业后师从王阳元院士和黄如院士攻读博士学位。她清楚地记得:读博伊始,王老师就把自己的新著《绿色微纳电子学》赠送给她,并语重心长地指出:未来集成电路产业和科学技术发展的驱动力是降低功耗,不仅以提高集成度(减小特征尺寸)为节点,也以提高能效比为标尺。

一般来说,为了追求芯片速度和性能的不断提升,晶体管的尺寸越来越小、集成度越来越高。但这也会导致芯片的功耗密度急剧增加,若不加以优化限制,甚至会接近核反应堆或火箭喷口的水平。随着万物互联智能时代的到来,物联网、工业互联网、边缘智能计算等呈指数级增长的终端对芯片功耗提出了更为严苛的要求。晶体管和电路芯片的功耗问题,已成为制约集成电路未来发展的一大瓶颈。

从那时起,黄芊芊便暗下决心:设计实现新型超低功耗晶体管,从基础器件层面着手破解这个难题。

选准技术路线,破解难题

在全面梳理国内外已有研究成果后,黄芊芊选择了一个突破口——隧穿场效应晶体管。

当时国际上主要有两大研究思路,一个是基于传统的硅材料,一个是直接换材料。相比之下,换材料更容易把器件的开态电流提上去,而且能更快地取得研究进展、发表论文。但是,这些新材料隧穿场效应晶体管与现有标准硅基工艺不兼容,难以实现大规模生产。

是在硅基这条“老路”上硬扛,还是跟随热点、在换材料上做文章?

在与两位老师商量之后,黄芊芊选择了前者。她心里很清楚,这其实是一条最难走的技术路线:基于硅材料的传统晶体管已经发展了几十年,结构设计和生产工艺已经非常成熟。这意味着在硅基工艺上隧穿器件可以突破的空间很小,面临的挑战无疑也更大。

为什么要选一条最难的路?黄芊芊的解释是“研以致用”:“尽管在新材料上做文章很有吸引力,也是重要的前沿热点,但这些新材料距离实际应用目前还比较远。在原有的硅基体系里去创新,能够更好地让成果落地。”

传统晶体管的功耗降低受制于一个物理极限——玻尔兹曼亚阈值摆幅极限。传统的MOSFET(金属—氧化物—半导体场效应晶体管)器件的亚阈值摆幅,在室温理想情况下的极限为60mV/dec。这意味着,获取3个数量级的输出电流开关比需要至少180mV的电源电压。该限制使得以MOSFET器件为基础的集成电路芯片不能无限制地通过减小工作电压来降低功耗。另一方面,为保证晶体管足够的电流驱动能力,需要在降低电源电压的同时降低MOSFET器件的阈值电压,但这又会引起器件关态电流的升高,导致静态功耗增加。

要解决这个矛盾,就必须要研发具有超陡亚阈值摆幅的新型超低功耗器件。基于量子带带隧穿机理的硅基隧穿场效应晶体管,当时国际同行已研究了五六年,其好处在于:理论上可以突破传统MOSFET的亚阈值摆幅极限,而且关态电流还特别低,对于静态功耗占主导的低频应用来说,有望大幅降低芯片功耗。

不过,有一利必有一弊:由于硅基隧穿场效应晶体管采用的是量子带带隧穿机理,所以其隧穿电流就会受限于隧穿几率,没有传统MOSFET的驱动电流高。而开态电流在很大程度上决定了晶体管运行的速度快慢——开态电流太低,性能就难以满足需求。

如何在保证极低关态电流优势的同时,解决开态低的问题?在两位老师的指导下,黄芊芊和同伴们提出了一种开创性的新理论——“混合控制”:采用传统肖特基注入机理解决开态低的问题,同时利用隧穿机理实现低关态和超陡亚阈值摆幅。

为验证这个新理论,黄芊芊花了整整一年时间,从头到尾做了一次完整的实验。那一年,她基本上是“白加黑”、连轴转:白天跑工艺间做实验,晚上总结经验教训。到紧要阶段更是常常连熬几个通宵。一年下来,人整个瘦了一圈。

有心人,天不负。最终的实验结果证明:“混合控制”的理论在实验上行得通!

另一个更实际的问题摆在面前:如何在工艺上做出非常陡的隧穿结?要知道,常规工艺较难做出理想陡峭的隧穿结,如果工艺上做不出来,就只能是纸上谈兵。这也是当时国内外同行报道的亚阈值摆幅比理论预期要差很多的关键所在。

针对现有工艺条件对亚阈值摆幅的限制,黄芊芊和同伴们提出了一个新机理——“结耗尽调制效应”:将常规栅结构改为横向条形栅结构,引入自耗尽作用,等效实现陡峭的带带隧穿结,进而显著减小器件的亚阈值摆幅。

此后,黄芊芊继续攻关,将“混合控制”与“结耗尽调制效应”的优势结合起来,进行结构与技术创新,提出并研制出新型梳状栅杂质分凝隧穿场效应晶体管,在室温下打破了国际上硅基隧穿器件的亚阈值摆幅纪录,器件综合性能为国际报道中同类器件最高。

抓住关键所在,走产业化之路

在学校的超净实验室做出隧穿场效应晶体管,只是万里长征的第一步。这个东西最终能不能成,还得在大生产线上做出来才行。

从2012年开始,黄芊芊与国内某顶尖集成电路制造商(以下简称CMC)合作,把在学校里研发的超低功耗隧穿场效应晶体管,拿到北京亦庄的生产线上去做。

隧穿场效应晶体管这个技术从结构上看似不复杂,但在国际工业界,仍未能采用标准工艺生产线制造出性能优异的隧穿器件。“上产线到底行不行?”从北大到亦庄有一个多小时的车程,坐在车里,黄芊芊一边忍受着头晕带来的不适,一边心里犯嘀咕。

在与CMC的技术团队反复交流讨论之后,她对原有的标准生产线工艺做了一些初步的设计调整,进行了几批流片,但是结果都不太理想。

回到学校,她屏息静气,先把可能的问题从头到尾梳理了几遍,然后重新评估:设计上哪些细节还需要调整,工艺上哪个环节还应该优化……找到症结所在后,她又对方案逐一修改、优化、改进。

在2015年博士毕业那年,黄芊芊和同伴们终于在CMC的产线上研制出世界上首个基于12英寸现行标准CMOS工艺平台的互补隧穿集成技术:在同一硅晶圆片上同时实现了性能优异的互补隧穿器件和标准CMOS器件的制备,隧穿器件的亚阈值摆幅在国际上基于制造厂商工艺的同类报道中首次实现低于60mV/dec,静态功耗比同尺寸MOSFET器件低3个数量级。

但是,从这一步到最终的目标仍有一定距离,还要面临优化工艺、解决良率等一系列问题。2015年—2017年做博士后期间,黄芊芊再接再厉,一门心思破解器件在产线上的涨落和可靠性等关键问题。

2017年9月,她博士后顺利出站,被北大聘为微纳电子学系研究员、博士生导师。她与北方集成电路技术创新中心等单位的科研团队联合申请了一项国家重点研发项目,朝着实现高可靠超低功耗晶体管技术产业化的目标继续行进。

“目前进展还不错,隧穿器件的电流开关比做到了业界国际领先,我觉得有望在未来几年内实现产业化应用。”黄芊芊说。

从2009年下半年算起,黄芊芊已经在超低功耗微纳电子器件这个研究领域跋涉了13年。

记者忍不住问她:“你为什么能一条道走到黑、坚持这么长时间?”

“就是觉得这个事情有意义。”黄芊芊说,从学界到产业界,现在还能坚持在硅基隧穿晶体管上做研究的,已经很少了。“因为我们一开始就是朝着产业化的方向做,所以能一直坚持下来,不然可能干个几年就要换方向了。”

“你在接手这个课题的时候,有没有想过其中的困难?”

“说实话,我没想过困难不困难的。”黄芊芊坦陈,“我就是大概知道我要干吗,其他的事情没怎么去想。但是当你真的要走到那儿的时候就会知道:这是多么不容易的事儿。”

“我知道它很难,但我也不会对未来想特别多,让自己焦虑或者怎样。”她的办法是,把目标拆解,一步一步往前推,争取每次比原来的自己更进步一点。

“就像爬珠穆朗玛峰,如果一开始就知道自己肯定上不去,你可能就不会上了。”黄芊芊说,“但我可以先到大本营,然后再慢慢往上走。走到半山腰、感觉自己爬不动的时候,我就会告诉自己:你都走到这份上了,干吗不再努力一把?”

黄芊芊跟记者分享了北大知名美学教授朱光潜先生的一句话:一个人的生活力之强弱,以能否朝抵抗力最大的路径为准,一个国家或是一个民族也是如此。

她特别喜欢这句话:“它简单质朴,没有什么华丽的辞藻,却把做事做人的道理讲透了。”

《 人民日报 》( 2022年12月05日 19 版)